### 4.4.16 Converters-Analog to Digital (A/D) and Digital to Analog (D/A) (i) Digital to Anlog Converter (DAC)

Module - IV

Analog output voltage  $V_A$  of an N-bit straight binary DAC converter is related to the digital equation

$$V_{\rm A}=K\left(2^{{\rm N}-1}\,b_{{\rm N}-1}+2^{{\rm N}-2}\,b_{{\rm N}-2}+...+2b_1+b_0\right)$$

where K = proportionality factor

$$b_{j} = +1 \text{ if } j \text{th bit of input 1}$$

$$= 0 \text{ if } j \text{th bit of input is 0}$$

$$j = 0 \text{ to } (N-1)$$

### Weighted resistor DAC:

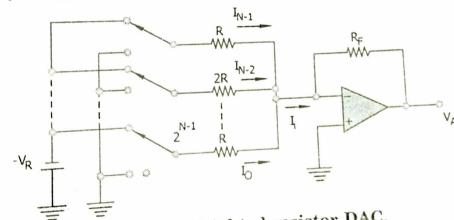

As the conversion D/A involves a weighted sum corresponding to the input to the converter, the summing circuit of Fig. 4.74 can be used as a DAC.

In this circuit,

$$I_i = I_{N-1} + I_{N-2} + ... + I_1 + I_0$$

Fig. 4.72. Weighted resistor DAC.

These currents can be expressed in terms of voltages as

$$I_{N-1} = V_{N-1}/R$$

$$I_{N-2} = V_{N-2}/2R$$

$$I_{0} = V_{0}/2^{N-1}R$$

$$V(0) = 0, \text{ and } V(1) = -V_{R}$$

Let Then

${\bf v}_{\rm N}=-\sigma_n\,\,{\bf v}_{\rm R}$  Switches in the circuit are digitally controlled causing  $b_n$  to acquire values 0 or 1.

Now,

$$I_{i} = -V_{R} \left[ \frac{1}{R} b_{N-1} + \frac{1}{2R} b_{N-2} + \dots + \frac{1}{2^{N-1}R} b_{0} \right]$$

The analog output of the circuit is given by

$$\begin{split} & V_{\rm A} = -R_{\rm F} I_i \\ & V_{\rm A} = V_{\rm R} \left[ \frac{R_{\rm F}}{R} \, b_{\rm N-1} + \frac{R_{\rm F}}{2R} \, b_{\rm N-2} + \ldots + \frac{R_{\rm F}}{2^{\rm N-1} R} \, b_0 \right] \\ & = K \left[ 2^{\rm N-1} \, b_{\rm N-1} + 2^{\rm N-1} \, b_{\rm N-2} + \ldots + 2^{\rm 1} b_1 + 2^{\rm 0} b_0 \right] \end{split}$$

where

$$K = \frac{R_F}{2^{N-1}R}$$

Hence the circuit is a DAC.

### R-2R ladder network:

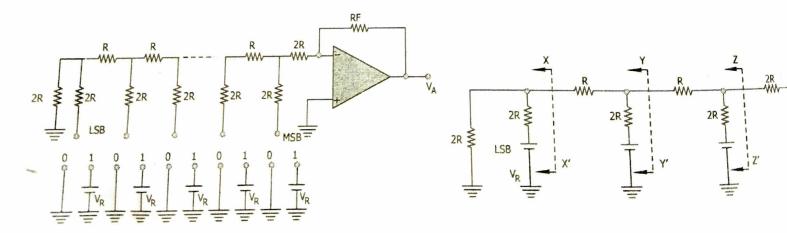

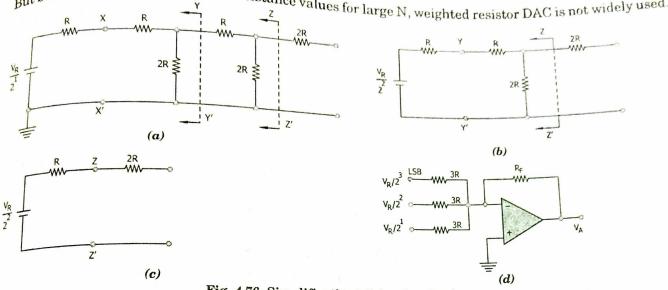

An R-2R ladder network [Fig. 4.75 (a)] uses resistors of only two values R and 2R. The inputs to the resistor network is applied through digitally controlled switches.

In a 3 bit R-2 R ladder DAC [Fig. 4.75 (a)] the input is assumed as 001. Applying Thevenin's theorem at XX', YY' and ZZ' we obtain circuits of Figs. 4.75 (a), (b) and (c) respectively. It is immediately seen that for input 001, voltage  $V_R/2^3$  is applied through 3R to the inverting terminal of the OPAMP.

Similarly for the digital input of 010 and 100, the equivalent voltages are  $m V_R/2^2$  and  $m V_R/2^1$  respectively with resistance 3R in each case. Therefore, we get equivalent circuit of Fig. 4.76 (d) wherein the voltage  $V_0$  is given by

$$V_0 = -\left[\frac{R_F}{3R} \frac{V_R}{2^3} b_0 + \frac{R_F}{3R} \frac{V_R}{2^2} b_1 + \frac{R_F}{3R} \frac{V_R}{2^1} b_2\right]$$

$$= -\left(\frac{R_F}{3R}\right) \left(\frac{V_R}{2^3}\right) \left[2^2 b_2 + 2^1 b_1 + 2^0 b_0\right]$$

This equation shows that analog output voltage is proportional to the digital input.

(a) R-2R tadder DAC network

(b) 3 bit R-2R ladder DAC network

DIGITAL CIRCUIT

OF CIRCUITS In general for N bit DAC.

$V_0 = V[2^N b_{N-1} + 2^{N-2} b_{N-2} + \dots + 2^1 b_1 + 2^0 b_0]$ where  $R_F = 3R$  and  $V_R = -2NV$

Number of resistors required for an N bit DAC (i) In case of R-2R ladder is 2N

(ii) In case of weighted resistor network is N

gut because of wide spread in the resistance values for large N, weighted resistor DAC is not widely used.

Fig. 4.76. Simplification of the circuit of

### (ii) Analog to Digital Converter (ADC)

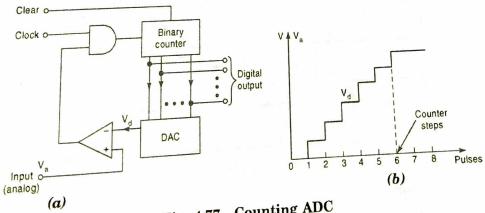

Counting ADC: This system is shown in Fig. 4.77 (a).

The clear pulse resets the counter to the zero count. The counter then records in binary form the number of pulses from the clock line. The clock is the source of pulses equally spaced in time. Since the number of pulses counted increases with time, the binary word representing this count is used as an input to the DAC, whose output is the staircase waveform shown in Fig. 4.77 (b). The comparator has an output which is 'HIGH' and the AND gate is open for transmission of clock pulses. When  $V_d$  exceeds  $V_a$ , the comparator output goes 'LOW' and AND gate is disabled. This stops the counting at the time when  $V_a \approx V_d$  and the counter can be read as the digital output representing analog input voltage.

Fig. 4.77. Counting ADC

### 8.13 SEMICONDUCTOR MEMORIES

SEMICONDUCTOR MEMORIAS

Memory Organization and Operation

Memory Organization and Operation

Memory Organization and Operation

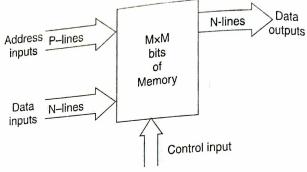

The basic element of a semiconductor memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of locations in a memory chip, each location being meant for one of location bein Memory Organization and Operation is a FLIT Memory Organization and Operation is a FLIT Memory Organization and Operation is a FLIT Memory Organization is a full for each location being meant for meant for one one of locations in a memory chip, each location being meant for one one of locations and the number of bits comprising the work vary one of locations and the number of locations and the number of locations and N is the meant of locations and N is the meant of locations are of locations. The basic element of a semiconductor in a memory chip, each the work for one in the work vary from the are a number of locations and the number of bits comprising the work vary from information. The number of locations and the memory and N is the number of bits. The in the memory and N is the number of locations are specified by two numbers and N is the number of locations. There are a number of locations and the number of under M and N as N × N ary from information. The number of locations are specified by two numbers M and N as N × N bits from memory. The size of a memory chip is specified by two numbers M and N is the number of bits. The memory. The size of a memory chip is specified by two numbers M and N as N × N bits are can be stored in the memory. information. The number of locations is specified by two nemons and N is the number of hits the memory. The size of a memory chip is specified by two nemons and N is the number of hits the memory. The size of a memory chip is specified by two nemons and N is the number of hits the number of hits at the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. The size of the number of locations available in the memory can be stored in the memory. memory. The size of a memory chip is a memory. The size of a memory available in the memory. The size of a memory of locations available in the memory. The specifies the number of locations available in the memory. The specifies the number of locations available in the memory of locations available in the specifies the number of locations available of N bits each constant of N bits In other words, this means that in words are 64, 256, 512, 12 years and the control words per chip are 64, 256, 512, 12 years are 1, 4 and 8 etc. Memories requiring higher number of words size are 1, 4 and 8 etc. Memories requiring higher number of words size are 1, 4 and 8 etc. word sizes can be formed by using these chips.

Fig. Block diagram of a memory device

Each of the M locations of the memory is defined by a unique address and therefore  $f_{0r}$  accessing the memory  $f_{0r}$  and  $f_{0r}$ Each of the M locations of the memory is defined by  $2^p = M$ . This set of lines is referred to as address of the M locations, P inputs are required, where  $2^p = M$ . For convenience, octal and the similar of the M locations, P inputs are required in the binary form. For convenience, octal and the similar of the M locations of the memory is defined by  $2^p = M$ . of the M locations, P inputs are required, where 2 and dress is specified in the binary form. For convenience, octal and hexa representations are commonly employed.

### Most commonly used memories

### 1. Sequentially accessed memory.

In the sequentially accessed memories, the memory location are accessed, for writing into on the sequentially accessed memories, the time required for accessing a memory location are accessed. In the sequentially accessed memory, and the sequentially accessed memory location (referent to a sequential fashion. Therefore the time required for accessing a memory location (referent to a sequential fashion.) as access time) for writing into or reading from is different for different locations.

Types. There are two types of sequentially accessed memories.

- (i) Shift registers: Shift registers can be either static or dynamic. In a static memory, the of the memory location do not change with time as long as power is on. On the other dynamic memories, the information is stored in MOS capacitors which changes with therefore it has to be refreshed at regular intervals. The dynamic memories are sin expensive, require less power have high packing density in comparison to static memorie therefore widely used in digital systems. However the cost of the additional circuitry re refreshing may increase the system cost.

- (ii) Charge coupled devices (CCD): The charge coupled devices are implemented u technology. These devices have high density and low cost.

The other mode of access of memory location is called as random-access in which the acc same for each memory location.

### 2. Read only memory (ROM).

The read and write memories is a random-access memory and is referred to as RAM. RAM. static or dynamic.

### 3. Read only memory (ROM).

It is meant only for reading the information from it.

### 4. Content addressable memory (CAM).

It is a special purpose random access memory which performs association operation in additional access memory which performs association operation access memory which access memory ac write operation.

Pd (FF) + tpd (AND)

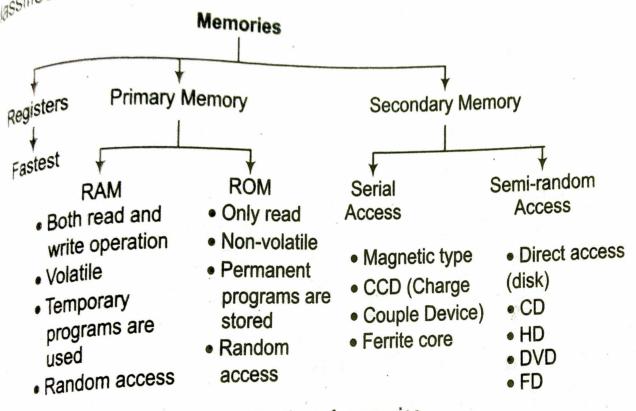

### **Memories**

Memories are used in the computer to store the data. Memories are

Classification of memories

### Random Access Memory (RAM)

The time taken to transfer information to or from any desired location is aways same hence it is called Random Access Memory (RAM).

$2^n \times m \rightarrow$  memory capacity

n: address line

m: data

## Classification of RAM

It is basically of two types

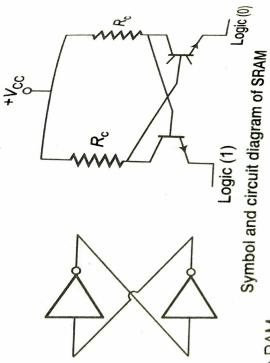

1. Static RAM

pigital

This is property of the proper

2. Dynamic RAM

### Comparison between SRAM and DRAM Circuit diagram of DRAM

ಕ

3

(#) MOSFET

Wr Data o

| Dynamic RAM | Data is stored in MOS capacity.             | Only MOSFET is used.                   | Slow.   | Dissipate less power. | Memory capacity is more. | Main memory.  | Refreshing is require.   |

|-------------|---------------------------------------------|----------------------------------------|---------|-----------------------|--------------------------|---------------|--------------------------|

| Static RAM  | Data is stored in flip flop like structure. | Can be implemented with BJT or MOSFET. | raster. | Dissipate more power. | Memory capacity is less. | Cache memory. | INO refreshing required. |

# ROM: Read Only Memory

- It is combinational circuit.

- It is also known as masked memory.

|                        | OR    | OR           | OR                 | OR          |

|------------------------|-------|--------------|--------------------|-------------|

| Comparison of Memories | Fixed | Programmable | Fixed              | Programable |

| rison of               | AND   | AND          | AND                | AND         |

| Compa                  |       | Fixed        | <b>Programable</b> | Programable |

|                        | ROM   | PROM         | X a                | PLA         |